Examen d'un Sommateur Complet Réalisé avec des Portes OU Exclusif et NAND :

4. - TROISIÈME EXPÉRIENCE : EXAMEN D'UN SOMMATEUR COMPLET

Un sommateur complet tient compte de la retenue du circuit sommateur précédent et génère bien entendu la retenue pour le circuit suivant.

Il dispose donc de trois entrées et deux sorties comme représenté à la figure 7-a.

La table de l'addition avec retenue située à la figure 7-b correspond en pratique, à celle obtenue lorsque l'on additionne entre eux trois nombres binaires de 1 bit, dont l'un est la retenue de la somme partielle précédente.

Examinons, par exemple, les trois sommes suivantes :

4. 1. - RÉALISATION DU CIRCUIT

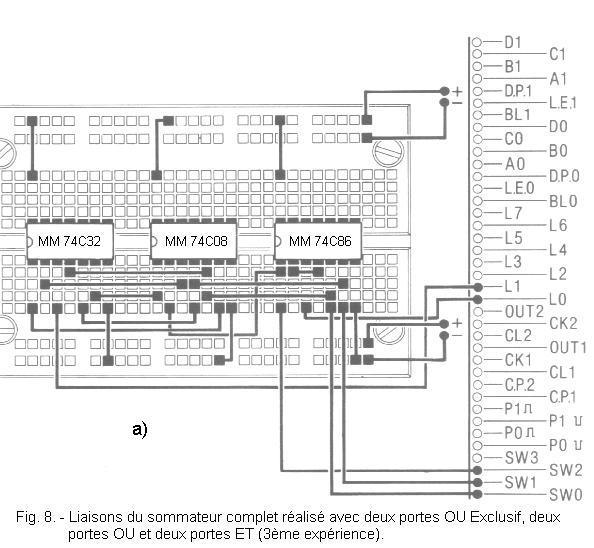

a) Laissez en place sur la matrice les circuits intégrés MM 74C86 et MM 74C08 et enlevez toutes les liaisons.

b) Insérez le circuit intégré MM 74C32 sur la matrice dans la position indiquée à la figure 8-a et effectuez les liaisons correspondantes.

Le schéma électrique du circuit est donné à la figure 8-b.

4. 2. - ESSAI DE FONCTIONNEMENT

a) Mettez le Digilab sous tension.

b) Essayez les différentes combinaisons des trois interrupteurs SW0, SW1 et SW2 et vérifiez à chaque fois que le circuit effectue bien la fonction somme selon la table de la figure 7-b.

Par exemple, avec SW0 sur la position 0, SW1 sur 1 et SW2 sur 1, L0 devra être éteinte et L1 allumée. Cette situation correspond à : 0 + 1 + 1 = 10.

c) L'expérience étant terminée, mettez hors tension le Digilab. En résumé, avec le circuit examiné, il est possible d'additionner trois nombres de 1 bit. Lorsque la somme et la retenue valent 1, on obtient le résultat maximum 11 équivalent au nombre décimal 3.

Dans les prochaines expériences, vous allez voir comment avec un seul sommateur complet associé à d'autres circuits, on peut additionner des nombres aussi grand que l'on veut.

![]() 5. - QUATRIÈME EXPÉRIENCE : EXAMEN D'UN SOMMATEUR

COMPLET RÉALISÉ AVEC DES PORTES OU EXCLUSIF ET NAND

5. - QUATRIÈME EXPÉRIENCE : EXAMEN D'UN SOMMATEUR

COMPLET RÉALISÉ AVEC DES PORTES OU EXCLUSIF ET NAND

Vous allez expérimenter maintenant un circuit qui effectue les mêmes fonctions que le circuit de la troisième expérience mais qui utilise cependant un circuit intégré de moins.

Le sommateur complet est appelé en anglais full adder.

5. 1. - RÉALISATION DU CIRCUIT

a) Enlevez de la matrice les liaisons et circuits intégrés relatifs à l'expérience précédente à l'exception du MM 74C86.

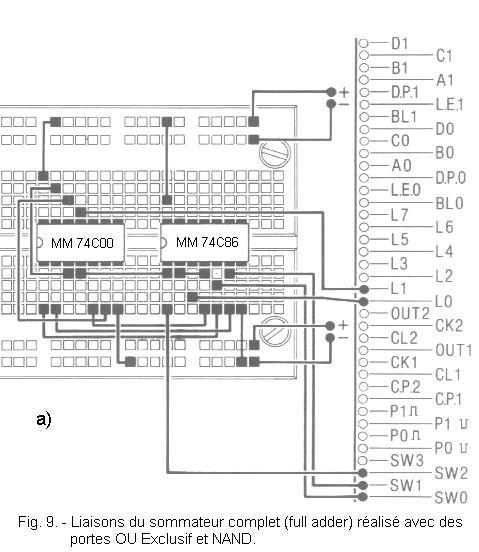

b) Insérez sur la matrice le circuit intégré MM 74C00 (quadruple NAND) et effectuer les liaisons indiquées à la figure 9-a.

Le schéma électrique du circuit réalisé est donné à la figure 9-b.

5. 2. - ESSAI DE FONCTIONNEMENT

a) Mettez sous tension le Digilab.

b) Essayez les différentes combinaisons des trois interrupteurs SW0, SW1 et SW2 et vérifiez à chaque fois que le circuit fonctionne comme un sommateur complet.

c) Les essais étant terminés, mettez hors tension le Digilab.

Si vous comparez le circuit expérimenté ici avec celui de l'expérience précédente, vous remarquez que ce second circuit, tout en étant différent et utilisant un nombre plus petit de circuits intégrés, remplit la même fonction.

Lorsque l'on doit réaliser une fonction logique, il est important de minimiser le nombre de circuits intégrés même si cela entraîne la nécessité d'employer des circuits intégrés plus complexes.

Dans la deuxième partie de cette pratique, vous aurez l'occasion de vous en rendre compte, en utilisant les multiplexeurs.

Cliquez ici pour la leçon suivante ou dans le sommaire prévu à cet effet. Cliquez ici pour la leçon suivante ou dans le sommaire prévu à cet effet. |

Haut de page Haut de page |

Page précédente Page précédente |

Page suivante Page suivante |

Nombre de pages vues, à partir de cette date : le 15 JUILLET 2019

Envoyez un courrier électronique à Administrateur Web Société pour toute question ou remarque concernant ce site Web.

Version du site : 10. 4. 12 - Site optimisation 1280 x 1024 pixels - Faculté de Nanterre - Dernière modification : 02 Septembre 2016.

Ce site Web a été Créé le, 14 Mars 1999 et ayant Rénové, en Septembre 2016.

Examen

d'un Sommateur Complet Réalisé avec des portes OU Exclusif et NAND

Examen

d'un Sommateur Complet Réalisé avec des portes OU Exclusif et NAND